為希科技

FPGA為傳統DSP應用提供靈活可重配置解決方案

FPGA為傳統DSP應用提供靈活可重配置解決方案

刊登日期 : 2007-09-17

訊號處理是連接現實世界與數位運算世界的橋樑。隨著使用數位訊號處理的演算法日益複雜,對這些演算法的性能要求也呈指數級上升。對要求低成本的大量設備,如行動電話、視訊轉換盒和電腦繪圖卡而言,此一要求正在推動開發極專用的特殊應用標準產品(ASSP)。然而對許多其它設備來說,實現高性能數位訊號處理的唯一選擇,是採用通用數位訊號處理器(DSP)以及最新的現場可編程閘陣列(FPGA)。

許多裝置中均使用了DSP。雖然DSP可透過軟體進行編程,但它的硬體架構很不靈活。DSP的性能受很多固定硬體架構的限制,如匯流排性能瓶頸、固定數量的乘法累加(MAC)模組、固定記憶體、固定硬體加速模組和固定數據頻寬等。因此,DSP的固定硬體架構並不適用於許多要求定製DSP功能的應用。

FPGA可以為傳統採用DSP的應用提供可重配置解決方案,並比DSP提供更高的吞吐量和原始數據處理能力。由於FPGA的硬體是可配置的,因此它能在提供完整硬體定製功能的同時實現各種DSP應用。用FPGA實現的DSP系統可具有定製架構、定製的匯流排結構、定製的記憶體、定製的硬體加速模組和可變數量的MAC模組。

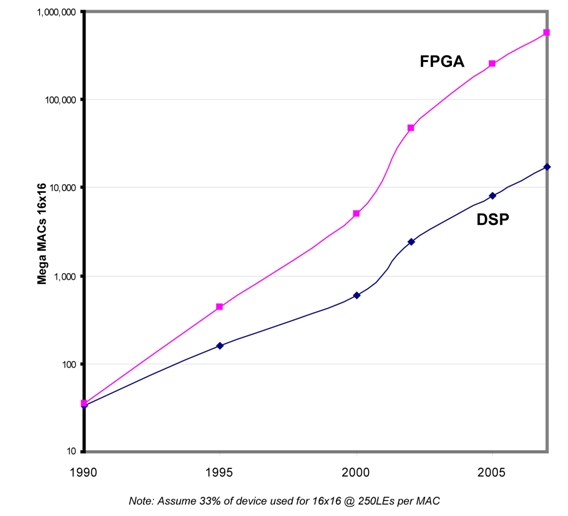

自2000年以來,FPGA就已經擁有了專用數位訊號處理(DSP)功能。過去六年來,FPGA提供的DSP性能已經提高了16倍之多,達到每秒500GMACS。相同期間,數位訊號處理器的性能只從1.6GMACS提高到了目前的8GMACS。而許多設備只需要少量的DSP性能,相當於類似Altera公司Cyclone II的FPGA所提供的性能。不過,對於要求許多數位訊號處理器的高性能設備來說,單一Altera Stratix III FPGA也能取代這些處理器,不僅能提供超過等效DSP的性能,還能顯著地減少系統功耗、電路板面積和成本。

對高性能DSP需求的關鍵驅動力來自無線通訊基礎設備、視訊廣播設備、醫療成像和軍事應用。FPGA已經成為能夠滿足這些要求的首選可編程DSP平台。

第三代通訊基地台平台是需要使用大量DSP的系統之一,它包含一片射頻卡和一片通道卡以及兩個主處理區。第三代無線通訊裝置大部份是寬頻產品,因此其射頻元件通常工作在線性範圍之外。先進的演算法有助於滿足遠高於傳統數位訊號處理器能力的處理要求。無線基礎設備中的主要設備目前主要依靠FPGA實現射頻線性化處理。

FPGA成為首選處理平台的另一個領域是WiMAX基頻處理,它採用的正交頻分多工(OFDM)技術需要巨大運算能力,只有特殊應用積體電路(ASIC)或FPGA才能滿足。由於ASIC太貴,開發風險很大,因此FPGA便成為WiMAX市場的贏家。

使FPGA成為DSP領域理想解決方案的關鍵性能包括有大量的乘法器、更高的內部記憶體頻寬、大量I/O頻寬,以及由可編程邏輯所帶來的獨特、靈活的FPGA架構等,目前還沒有其它可編程技術能提供相同的DSP性能。與其它半導體解決方案相較,FPGA可在更低功耗下提供最高性能的可編程DSP功能,同時還能降低系統成本和減少電路板面積。

系統設計師可以用一顆或幾顆FPGA,開發出一款原本需要數十顆DSP和多片電路板才能實現的板級設計。由於採用相同封裝的FPGA可支援垂直升級,因此能在無需多電路板設計條件下,輕易將單板和系統設計從低階升級到高階功能。這種靈活性是很大的優勢,因為它能減少產品的工程設計和驗證成本。

以Stratix III FPGA系列元件為例,它為FPGA的DSP新增了許多功能,如密度倍增、性能提升、功耗降低、I/O性能增強等,另外,DSP模組也有了重大創新。

增加DSP模組中的內建乘法器數量(最多是896個18×18乘法器)是一項重大創舉。它允許在更小的矽晶片面積中整合更多乘法器,同時能降低功耗。DSP模組通常是針對性能、靈活性和低功率進行最佳化的硬體模組。DSP矽模組有兩項限制條件:週邊數量和使用面積大小。

圖1:近年來FPGA與DSP性能的演變情況

圖2. 第三代通訊基地台處理架構圖

DSP模組的週邊有144根輸入線和144根輸出線,以及一些控制訊號。DSP模組的面積可以實現4個18×18的乘法器以及相對應的輸入輸出訊號。而對矽晶片與系統級DSP模組如何發展的研究,則是以特殊應用需求和向65nm製程技術轉移所衍生的效應為基礎。

在晶片級,改變週邊與DSP模組面積的比例可形成更多I/O或更多的模組級邏輯。在系統級,對DSP演算法的調查顯示,乘法器邏輯的主要使用者是濾波和轉換演算法,它們都仰賴乘法累加作業來滿足大部份處理要求。在需要時,透過最佳化DSP模組的核心面積,可以增加一倍的乘法累加作業次數,降低相對於整體運算的週邊I/O要求。透過在一個DSP模組中完成更多的DSP演算法,就能提升整體晶片效率。

圖3顯示了一個具備8個18×18乘法器和相關暫存器、累加器以及整數化/飽和電路的DSP模組如圖3所示。乘法器的使用受限於DSP模組的輸出線,而非邏輯面積。與競爭架構相較,這種架構可以使矽晶片效率約提高50%。

圖3:Stratix III DSP模組架構

模組的整體DSP功能減少了使用乘法累加作業的標準演算法,如有限脈衝響應(FIR)濾波器或複雜乘法器,同時,由於不需要使用可編程邏輯矩陣,因此也減少了整體功率和資源消耗。當乘法累加作業作為演算法的一部份被包含在內時,可以大幅增加18×18乘法器的數量。

對許多系統架構來說,FPGA的一項優勢是垂直升級特性。這種特性能讓用戶使用單一電路板,無需重新設計就能支援靈活的處理性能和成本。系統架構師可以運用此一功能開發出具有各種價位和性能的產品,卻不會顯著影響開發成本或導致庫存。另外,隨著Altera推出HardCopy結構化ASIC,當需要考慮大量和高性價比結構時,也能獲得額外的性價比。

無線基礎設備是良好運用這種靈活性的範例。用於靈活通道卡中的FPGA支援各種標準,透過垂直升級還能支援各種通道密度。一個基地台可被配置為最少的通道數,也可以使用相同的基礎架構對通道進行大量擴充,只需改變FPGA的選擇。在許多發展中國家,注意力往往放在更靈活、可升級和具備豐富服務特性的設備上,這些設備需要FPGA的這種靈活性。在這些對價格特別敏感的地區,同一產品中的標準化功能可以使用HardCopy結構化ASIC以更低成本來實現。採用這種解決方案的供應商將擁有極大技術優勢,無需增加工程成本就能提高業務的靈活性。

FPGA的I/O頻寬比DSP頻寬大得多。I/O頻寬是滿足系統處理要求的關鍵要素,而頻寬又受數據輸入輸出以及外部數據記憶體的影響。在對記憶體有很高要求的應用領域,Stratix III記憶體介面支援400MHz的DDR3記憶體,這個外部記憶體頻寬要比目前最先進的DSP高16倍。

由於系統級開發工具可協助系統架構師實現靈活性、可發展性、可維修性和高性能訊號處理及控制架構,因此FPGA在過去幾年中發展非常迅速。這些工具套件包括DSP系統建模工具、系統合成工具、控制處理IP、自動化C語言到硬體加速和DSP最佳化的應用IP。設計師利用這些工具,就能快速設立真正獲得最佳化以滿足系統要求的高性能架構。在可垂直升級和HardCopy結構化ASIC的支援下,系統架構師可以根據產品要求實現可擴展性能,開發出各種產品以滿足不同市場要求,同時提高實際的生產效益。

目前,在開發FPGA內部架構時所需的IP與工具均已完備,但基於一些其他原因,系統架構中仍需採用標準的第三方處理器。當第三方處理器與FPGA一起使用時,它能透過一種被稱為FPGA協同處理的架構技術顯著提高系統性能,同時降低系統成本、功耗和電路板面積。在FPGA協同處理過程中,FPGA可以從第三方處理器卸載任務繁重的演算法。許多系統使用控制處理器、數位訊號處理器和一個或多個FPGA(在FPGA中執行主要的處理負載),其中控制和DSP用於滿足傳統軟體、作業系統要求,或是針對最終應用(如Windows GUI控制)的處理。

高性能系統的核心訊號處理將逐漸轉向FPGA。FPGA具備其他半導體元件無法提供的高度可編程DSP性能,加上垂直升級以及針對低成本元件的HardCopy技術,能以靈活的系統架構滿足性能、低功耗、低成本和產品對廣度及壽命的要求。

作者:Paul Ekas

資深產品經理

Altera公司

全文摘錄自:電子工程專輯http://www.eettaiwan.com/ART_8800479676_681521_TA_8c3336bf.HTM